技术天堑:横亘在NAND与DRAM之间的制造深渊

伴随AI产业爆发式增长,市场对内存芯片的需求持续激增,半导体供应链重组的相关传闻也随之升温。近期,有消息披露,武汉某国产NAND存储厂商正计划借助新建晶圆厂的产能,跨界布局DRAM及HBM制造领域,且据称已成功研发出LPDDR5工程样品。这一消息看似承载着国产存储突围的期待,实则在业内人士眼中,更像是一场忽视产业规律、过于理想化的豪赌。

多位半导体制造专家及行业分析师一致指出,考量到DRAM与NAND在底层物理逻辑、制造工艺以及资本投入强度上的巨大差异,这家厂商的跨界尝试,本质上与“从零起步”毫无二致,其成功概率微乎其微。

作为半导体产业中技术门槛最高、制造难度最大的芯片品类之一,DRAM内存芯片的研发与生产难度,丝毫不逊色于CPU、GPU等高端逻辑芯片。回顾全球存储产业的发展历程,三星、美光、海力士三大巨头的崛起路径高度一致:均是先在DRAM技术领域站稳脚跟、确立统治地位后,才凭借深厚的技术积淀“降维拓展”,切入NAND闪存领域。

这种“先DRAM后NAND”的发展路径绝非偶然,而是行业规律的必然体现。业内普遍认为,DRAM在技术精度、制造工艺等核心层面的要求,远高于NAND闪存。从技术难度更高的DRAM领域,向下延伸至NAND领域,属于顺理成章的业务拓展;反之,一家专注于NAND领域的厂商,试图逆向突破DRAM的技术壁垒,在全球半导体产业史上,至今尚未有过成功的先例。

追求极致的微缩工艺VS追求密度的堆叠艺术

尽管同属存储芯片范畴,但DRAM与NAND的产品功能、工作原理截然不同,这也导致二者的技术演进路线出现本质分歧。DRAM属于内存芯片,与CPU等计算单元直接相连,核心作用是临时存储CPU所需数据,属于易失性存储,一旦断电,存储的数据便会瞬间丢失;NAND则属于外存芯片,不与CPU直接连接,主要用于长期存储海量文件,属于非易失性存储,即便断电也能长久保留数据。

由于在计算体系中,DRAM更贴近核心的CPU,其性能要求也更为严苛——DRAM的读写速度约为NAND的3000倍,单位单价也远高于NAND。在摩尔定律持续演进的当下,二者的技术发展方向已彻底分化:NAND的核心演进路径是垂直堆叠,如同建造摩天大楼,关键在于实现更高层数的垂直堆叠(如232层及以上),核心挑战集中在立体结构的稳定性与精密加工;DRAM的演进则主要依靠光刻技术微缩,类似在一颗大米上雕琢《清明上河图》,核心难点的是在极小的微型电容中稳定保存电荷。

这一本质分歧决定了,现有NAND生产线无法通过简单的软件升级或局部改造,实现DRAM的量产。行业数据显示,两类产线的设备通用性不足50%,将一座NAND晶圆厂改造为DRAM工厂,在资本投入效率上极不划算,其成本与难度几乎等同于新建一座全新的DRAM工厂。

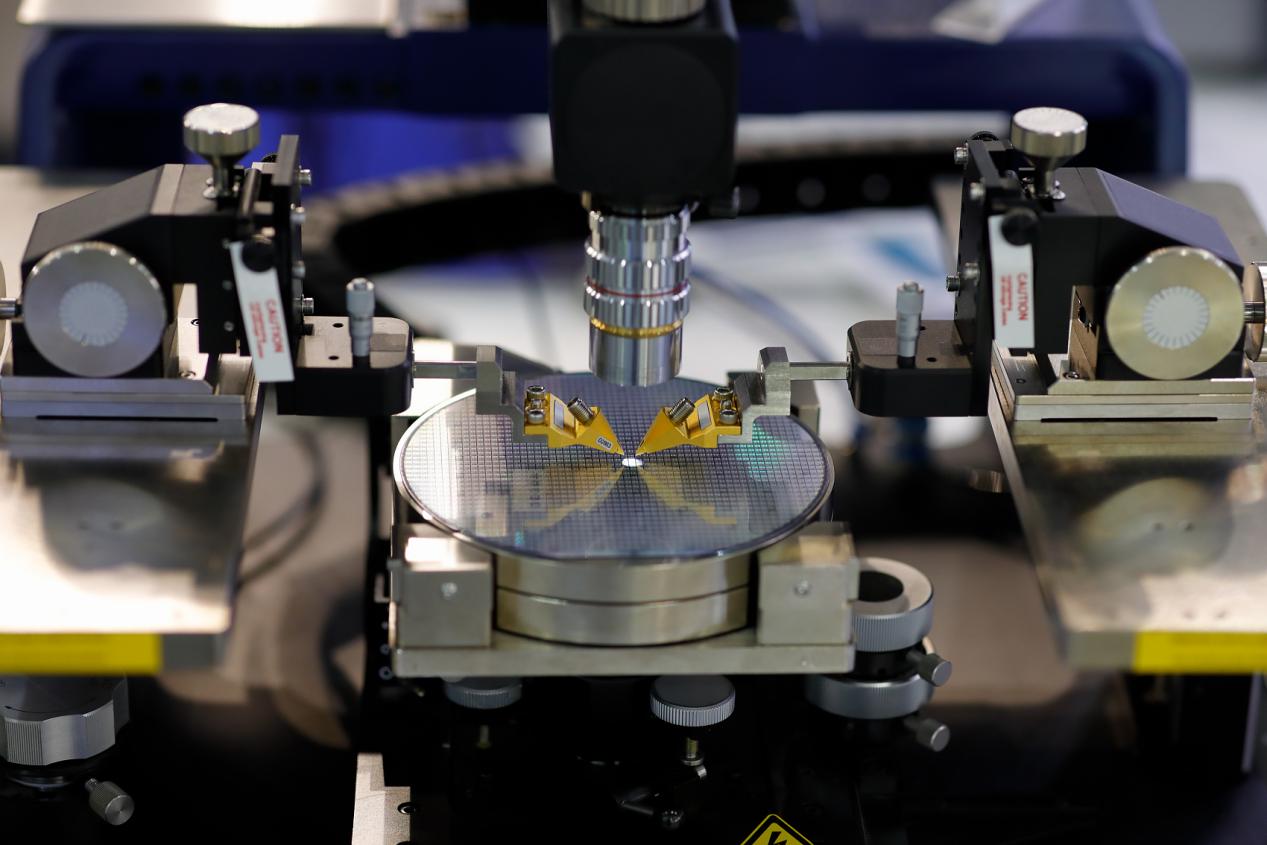

量产鸿沟:历史证明无法绕行的必经之路

对于传闻中提及的LPDDR5工程样品,专业分析师提醒,市场不应过度解读实验室样品的意义。在半导体行业,实验室样品与商业化量产之间,横亘着一道被称为“良率死亡之谷”的巨大鸿沟,而DRAM的这道鸿沟尤为宽阔。

作为对缺陷密度极度敏感的器件,DRAM的良率爬升周期通常长达数年,需要持续的技术优化与大量的资金投入。此外,当前DRAM市场已形成高度成熟的寡头垄断格局,三大巨头牢牢掌控市场主导权。对新进入者而言,最大的风险并非仅来自技术层面,更在于商业逻辑的失衡:用NAND业务相对微薄的利润率,去支撑DRAM研发与量产所需的巨额现金流消耗,这种模式在财务层面被普遍视为高风险策略。

诚然,全球半导体供应链多元化的需求日益迫切,但这并不能改变半导体制造的客观物理规律。面对复杂的DRAM工艺节点与稳固的专利壁垒,市场传闻显然低估了从NAND跨界至DRAM所需的工程技术深度。对于投资者与行业观察家而言,清晰区分“早期实验性探索”与“实质性产能转移”至关重要。在高度专业化的半导体行业,“术业有专攻”依然是衡量企业核心竞争力的最高标准,忽视产业规律的理想化豪赌,终究难以落地生根。

免责声明:本网站有部分内容均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,若因作品内容、知识产权、版权和其他问题,请及时提供相关证明等材料并与我们联系,本网站将在规定时间内给予删除等相关处理.

猜你喜欢