深度解析:为何NAND厂商难以凭借堆叠技术跨界HBM

AI产业的爆发式增长,让HBM(高带宽内存)一跃成为全球半导体产业的战略核心,一举一动皆牵动市场神经。近日,以武汉某厂商为代表的国产NAND企业,凭借其在混合键合技术上的深厚积淀与成熟的“堆叠”工艺,已然具备跨界切入HBM领域的核心技术底气。这种说法在资本层面颇具迷惑性,似乎为国产HBM突围指明了一条捷径,但在工程实践与技术逻辑层面,却存在一个致命误区——它彻底混淆了NAND与HBM两种“堆叠”工艺的核心本质,将看似相似的技术概念,误判为可直接平移的技术路径。

事实上,二者之间的技术鸿沟,远比外界想象的更为深邃,所谓“凭借NAND堆叠优势进军HBM”,本质上是一场脱离产业实际的技术误读。本文将深入拆解两种“堆叠”工艺的核心差异,揭示这场误读背后的技术逻辑真相。

本质分野:NAND与HBM堆叠的核心逻辑差异

技术外行所见皆为“堆叠”,而内行眼中却是两种迥异的工业语言。其根本区别在于集成的基本单元:

NAND(如Xtacking技术)的路径是“晶圆对晶圆”:它如同将两张完整的、绘制好电路的地毯(存储晶圆与逻辑晶圆)精密对准,然后整体键合在一起。它的优势在于大规模、高效率的二维平面集成,核心挑战在于整片晶圆级别的超高超净间工艺控制和对准精度。

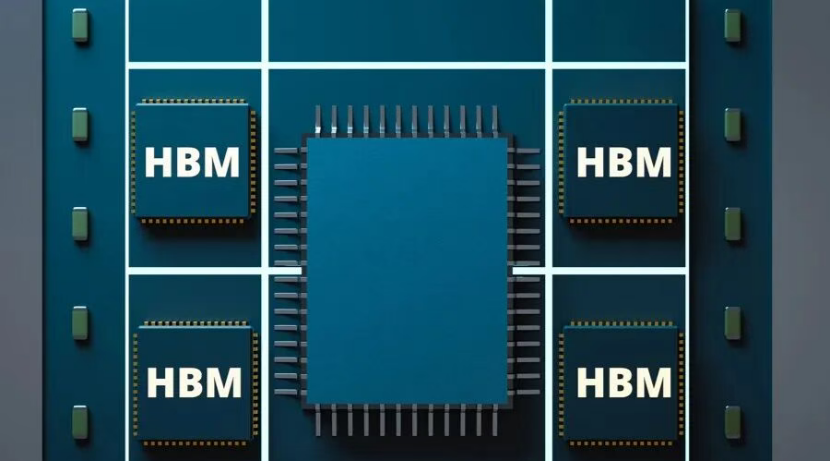

HBM的路径是“芯片对晶圆”:它首先需要将制造好的DRAM晶圆切割成独立的方形芯片,通过严格测试筛选出性能合格的“已知好粒”,再像镶嵌马赛克或搭建乐高积木一样,将这些微小的芯片一颗颗精准地拾取、定位、堆叠到另一片基础晶圆上。其核心挑战在于微米级精度的芯片级处理、测试分选和异构集成能力。

简而言之,NAND厂商擅长的是“铺整张地毯”,而HBM要求的是“镶嵌精密马赛克”。这两套技术体系所需的设备机台、工艺控制逻辑和精度标准完全不同,无法简单复用或“平移”。

良率困境:两种堆叠模式的商业可行性鸿沟

为何HBM不能采用NAND的W2W模式?一道简单的数学题便能揭示其商业上的不可行性。

假设单层DRAM晶圆的良率已达到非常理想的90%。若采用W2W方式堆叠8层HBM,最终产品的良率将是各层良率的连续乘积:0.9的8次方,约等于43%。这意味着超过一半的成品将成为废品。若堆叠至12层,良率将骤降至28%。这种因层数叠加导致的良率指数级崩塌,在任何商业生产中都是灾难性的。

而D2W路线的核心智慧在于引入了KGD策略。它在堆叠前就对每一颗芯片进行测试,只选用已知的合格芯片进行组装。这样,虽然增加了测试和分选的成本与工序,却成功将良率计算从恐怖的“连乘”变成了可控的“叠加”,确保了大规模量产的经济性。显然,NAND的W2W这把“锤子”,完全砸不开HBM这颗需要对每颗“零件”进行前置质检的“核桃”。

核心前提:DRAM芯片是HBM量产的必破难关

即便跨界者通过巨额投资购置了D2W全套设备,攻克了堆叠工艺,HBM制造仍有一个无法绕过的前提:必须首先拥有自主生产的高性能、高良率DRAM芯片。

HBM的本质,是将多颗顶级DRAM芯片通过硅通孔等先进互连技术集成。键合封装技术是“连接的艺术”,而DRAM芯片本身则是“建筑的基石”。如果基础芯片的性能(如速度、带宽、功耗)达不到严苛的JEDEC标准,或在堆叠后无法解决惊人的散热问题,那么再精湛的封装技术也只是将一堆平庸或不合格的“砖块”牢固地粘合在一起,无法构筑起算力的“摩天大楼”。

近期关于LPDDR5工程样品的传闻,与HBM量产之间更是相隔数重山。从工程样品到稳定量产需要穿越漫长的“死亡之谷”;且HBM堆叠的是特定的高速DDR颗粒,与移动端LPDDR设计不同。将“拥有芯片”和“掌握堆叠”简单等同于“能造HBM”,是一种危险的认知简化。

产业启示:走稳国产HBM突破之路

HBM作为半导体工业皇冠上的璀璨明珠,从来不是单一工艺的简单叠加,而是DRAM芯片设计、尖端制造与先进封装技术的集大成者。外界所关注的“堆叠”,只是其最显性、最末端的一道工序,绝非决定成败的核心环节。真正的核心竞争力,根植于对DRAM芯片物理极限的持续探索、对良率控制的极致追求,以及对异构集成工艺的深度打磨。

对于立志突破HBM技术壁垒的国产厂商而言,产业规律早已指明了清晰的突破路径:必先扎实攻克高性能DRAM芯片的自主设计与规模化量产难题,筑牢“基石”;再逐步攻坚D2W等尖端异构集成工艺,掌握“连接的艺术”。跳过DRAM这一核心前提,妄图凭借NAND堆叠技术实现HBM“弯道超车”,无疑是脱离产业底层逻辑的技术浪漫主义。

免责声明:本网站有部分内容均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,若因作品内容、知识产权、版权和其他问题,请及时提供相关证明等材料并与我们联系,本网站将在规定时间内给予删除等相关处理.

猜你喜欢